# A Monolithically Integrated 120-GHz InGaAs/InAlAs/InP HEMT Amplifier

R. Lai, *Member, IEEE*, H. Wang, *Member, IEEE*, K. L. Tan, *Member, IEEE*, D. C. Streit, *Senior Member, IEEE*, P. H. Liu, J. Velebir, Jr., S. Chen, *Member, IEEE*, J. Berenz, and M. W. Pospieszalski, *Fellow, IEEE*

**Abstract**— We report the design and gain performance for a two-stage 120-GHz monolithically integrated amplifier using 0.1- $\mu\text{m}$  gate length pseudomorphic  $\text{In}_{0.60}\text{Ga}_{0.40}\text{As}/\text{In}_{0.52}\text{Al}_{0.48}\text{As}/\text{InP}$  HEMT's. The two-stage amplifier demonstrated 10–12 dB gain measured between 119.5 to 123.5 GHz. To the best of our knowledge, this is the first demonstration of a monolithically integrated InP HEMT amplifier reported at D-band.

## I. INTRODUCTION

DEVELOPMENT of high-performance receivers at *D*-band (110–170 GHz frequency range) is important for applications in radars, radiometer, remote sensing, and imaging. The potential system advantages with higher frequency operation include higher resolution images, smaller antenna aperture, better compactness, lower power, and lighter weight. InGaAs/InAlAs/InP High Electron Mobility Transistors (InP HEMTs) have demonstrated the best gain and noise performance on a discrete device level at millimeter-wave frequencies due to its intrinsic material properties [1]–[4]. Single-stage and two-stage hybridly integrated InP HEMT amplifiers at 140 GHz have demonstrated 7.3 and 9.3 dB gain, respectively [1]. Here, we report the gain characteristics of a monolithic two-stage 120-GHz amplifier using 0.1- $\mu\text{m}$  gate length pseudomorphic  $\text{In}_{0.60}\text{Ga}_{0.40}\text{As}/\text{In}_{0.52}\text{Al}_{0.48}\text{As}/\text{InP}$  HEMT (PM InP HEMT) technology.

The PM InP HEMT structure [1] is grown using molecular beam epitaxy on a 2-inch InP substrate. Details on device design considerations have been presented elsewhere [5]. For operation at very high frequencies, particular attention was paid to minimize device parasitic capacitances and resistances. Discrete 0.1- $\mu\text{m}$  gate length PM InP HEMT has demonstrated transconductances of 1400 mS/mm, cutoff frequencies of 240 GHz, and maximum oscillation frequencies of 400 GHz at a drain bias of 1 V. A measured gain of 12.2 dB at 94 GHz and 7.3 dB at 140 GHz [2] were obtained from hybrid amplifiers using these devices, which give more validity to the extrapolated  $f_T$  and  $f_{\max}$  numbers. We have also demonstrated a monolithically integrated 75–110 GHz 4-stage balanced InP HEMT amplifier with  $23 \pm 3$ -dB gain across the entire band [6].

Manuscript received February 4, 1994.

R. Lai, H. Wang, K. L. Tang, G. I. Ng, D. C. Streit, P. H. Liu, J. Velebir, Jr., S. Chen, and J. Berenz are with TRW Advanced Microelectronics Laboratory, Redondo Beach, CA 90278 USA

M. W. Pospieszalski is with the National Radio Astronomy Observatory, Charlottesville, VA 22903 USA.

IEEE Log Number 9402171.

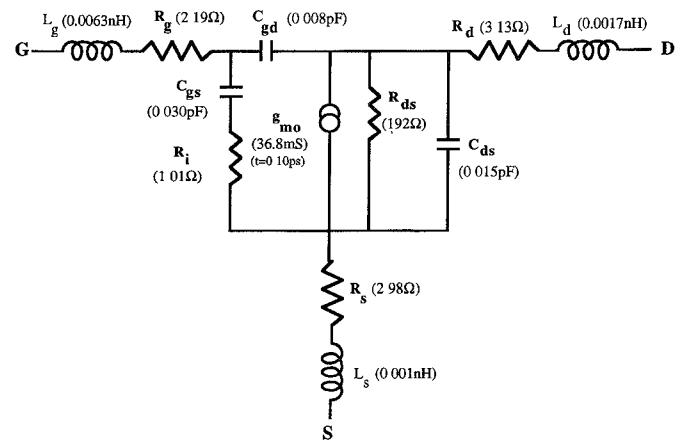

Fig. 1. Equivalent circuit of 0.1- $\mu\text{m}$   $\times$  40- $\mu\text{m}$  PM InP HEMT biased at 1.0 V drain bias and 70%  $\text{I}_{\text{ds}}$  at peak  $\text{G}_m$ .

## II. CIRCUIT DESIGN AND PERFORMANCE

The linear small signal model for a 0.1- $\mu\text{m}$  gate length four finger, 40- $\mu\text{m}$  gate width PM InP HEMT [1], [2] used in this 120-GHz LNA design are obtained from the measured small signal *S*-parameters up to 50 GHz using standard curve fitting techniques. The noise model parameters are also obtained using curve fitting techniques from the measured noise parameters up to 26 GHz. The resulting parameters are consistent with the estimated values based on device physical dimensions and parameters.

The *D*-band amplifier is a two-stage single-ended design and each stage uses a 40- $\mu\text{m}$  PM InP HEMT (Fig. 1). The input and interstage matching networks are designed for low noise performance and are constructed by cascading high-low impedance microstrip lines. Edge coupled lines are used for dc blocking and radial stubs are employed for RF bypass. Shunt  $N+$  bulk resistors are included in the bias networks for amplifier stability. The InP substrate was thinned to 70  $\mu\text{m}$  and a wet chemical etching process is used to fabricate back side via holes for grounding. The 70- $\mu\text{m}$  substrate thickness was chosen to minimize the wet etched via hole size, which minimizes the source inductance of the device.

For the 120-GHz amplifier development, a design procedure using full-wave EM analysis for the passive structures to eliminate the uncertainties due to quasi-static models was incorporated in this 120-GHz monolithic amplifier development. The design/analysis methodology, together with the device modeling procedure, was documented in a previous paper

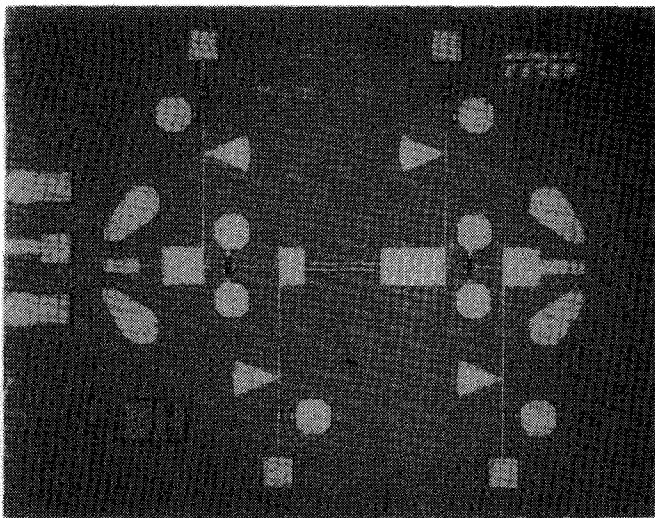

Fig. 2. Photograph of the 2-stage 120-GHz PM InPHEMT MMIC amplifier with a total chip size of  $1.7 \times 1.6 \text{ mm}^2$ .

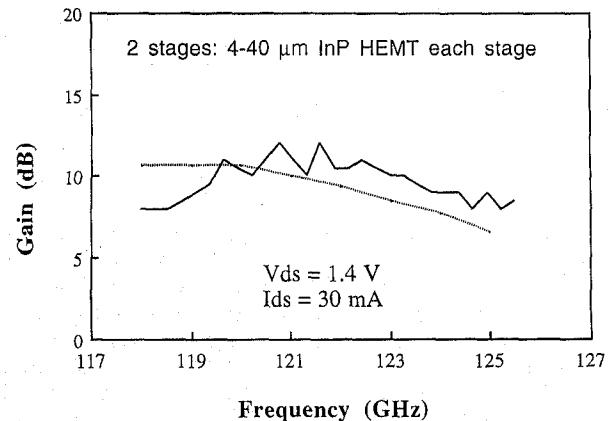

[8]. A picture of the 120-GHz amplifier with a total chip size of  $1.7 \times 1.6 \text{ mm}^2$  is shown in Fig. 2. The circuit was first tested on-wafer from 100–120 GHz using a verified *W*-Band on-wafer probe test set [9] for a quick evaluation of the circuit. The measured gain was 8–12 dB from 100–118 GHz. The chip was then tested from 118–125 GHz in a *D*-band test fixture. Finline waveguide to microstrip transitions were fabricated on 3-mil quartz substrates. The measured insertion loss for a pair of back-to-back transitions was 2 dB at 120 GHz with a return loss  $>15$  dB. The amplifier's measured gain characteristics are shown in Fig. 3. The amplifier demonstrates 10–12 dB gain from 119.5–123.5 GHz after correction for the transition losses. The measured gain characteristics correspond reasonably well with the simulated results, which show a peak gain of about 11 dB from 118 to 120 GHz. In this study, we were unable to measure the noise performance of the amplifier because verifiable noise measurement systems are not available in this frequency range. The overall DC power dissipation of the circuit was only 42 mW ( $V_d = 1.4$  V,  $I_{d\text{total}} = 30$  mA).

### III. SUMMARY

We have successfully demonstrated a monolithic *D*-band two-stage amplifier using 0.1- $\mu\text{m}$  gate length pseudomorphic  $\text{In}_{0.60}\text{Ga}_{0.40}\text{As}/\text{In}_{0.52}\text{Al}_{0.48}\text{As}/\text{InP}$  HEMT technology. The amplifier tested in a *D*-band fixture showed a measured gain of 10–12 dB from 119.5 to 123.5 GHz. This is believed to be the highest frequency monolithic amplifier ever reported.

Fig. 3. Measured gain characteristics for the 2-stage 120-GHz amplifier with  $V_d = 1.4$  V and  $I_d = 30$  mA.

### ACKNOWLEDGMENT

The authors would like to acknowledge A. Freudenthal for electron-beam lithography, L. Go and R. Dia for wafer fabrication, and the members of the Advanced Microelectronics Laboratory and RF Product Development Laboratory for their support in this work.

### REFERENCES

- [1] K. Tan *et al.*, "140 GHz 0.1  $\mu\text{m}$  Gate Length Pseudomorphic InAlAs/InGaAs/InP HEMT," in *Proc. 1991 IEDM*, 1991, Washington DC, p. 239.

- [2] P. D. Chow *et al.*, "W-band and *D*-band Low Noise Amplifiers Using 0.1  $\mu\text{m}$  Pseudomorphic InAlAs/InGaAs/InP HEMTs," in *Proc. 1992 Int. Microwave Symp.*, 1992, Albuquerque, NM, p. 807.

- [3] L. D. Nguyen *et al.*, "50 nm Self-Aligned Gate Pseudomorphic AlInAs/GaInAs High Electron Mobility Transistors," *IEEE Trans. Electron Devices*, vol. 39, p. 2007, 1992.

- [4] K. H. Duh *et al.*, "A Super Low-Noise 0.1  $\mu\text{m}$  T-gate InAlAs/InGaAs/InP HEMT," *IEEE Microwave and Guided Wave Lett.*, vol. 1, p. 114, 1991.

- [5] R. Lai *et al.*, "A High Performance and Low DC Power V-band MMIC LNA Using 0.1  $\mu\text{m}$  InGaAs/InAlAs/InP HEMT Technology," *IEEE Microwave and Guided Wave Lett.*, vol. 3, p. 447, Dec. 1993.

- [6] H. Wang *et al.*, "A Monolithic 75–110 GHz Balanced InP-based HEMT Amplifier," *IEEE Microwave and Guided Wave Lett.*, vol. 3, 1993, p. 381.

- [7] H. Wang *et al.*, "A High performance *W*-band monolithic InGaAs pseudomorphic HEMT LNAs and design/analysis methodology," *IEEE J. Solid State Circuits*, vol. 28, p. 988, 1993.

- [8] H. Wang *et al.*, "High performance *W*-band monolithic InGaAs pseudomorphic HEMT LNAs and design/analysis methodology," *IEEE Trans. Microwave Theory Tech.*, vol. 40, p. 417, 1992.

- [9] S. Chen *et al.*, "A *W*-band automated on-wafer probing noise figure measurement system," in *41st Automated RF Tech. Group Conf. Dig.*, June 1993, Atlanta, GA, p. 48.